概要

本文主要基于 Altera Stratix10 和 Agilex 7 FPGA 在客户实际应用中遇到的电源管理及配置问题,系统梳理了典型故障案例、解决方案与调试建议。内容主要涵盖:

电源与配置的流程

6 大实战案例解析

关键检查方向与调试建议

Stratix10 和 Agilex 7 是 Altera 的两款高端 FPGA (现场可编程门阵列) 产品系列。

Stratix10:

Altera Stratix系列可帮助交付性能高端、品质优异的产品。Stratix10 FPGA 和 SoC FPGA 在性能、能效、密度和系统集成方面都具有创新优势,工艺为 Altera 14nm 器件。Stratix10 器件采用变革性的英特尔Hyperflex FPGA 架构,并结合英特尔 Embedded Multi-Die Interconnect Bridge (EMIB) 专利技术、Advanced Interface Bus (AIB) 和不断壮大的芯粒产品组合,性能比上一代高性能 FPGA 提升高达 2 倍。

Agilex 7:

Altera Agilex 7 FPGA 为 Altera 10nm 器件,采用第二代 Hyperflex FPGA 架构,支持 PCIE Gen5 X16,116Gpbs PMA4,32GBHBM2E,400G 硬 MAC,DDR5,最大 4.1 百万门逻辑资源等,广泛应用于数据中心加速、边缘计算、高带宽网络通信、高端仪器仪表等行业,以优异的性能广受客户喜爱。

Altera Stratix10 和 Agilex 7电源配置流程详解

下图 (图1) 为 Altera Stratix10/Agilex 7 电源管理及配置的界面。该系列支持的配置模式如下:

Avalon streaming (Avalon-ST)

JTAG

Configuration via Protocol (CvP)

Active Serial (AS) normal and fast modes

图1 Altera Stratix 10/Agilex 7电源管理及配置界面

Altera Stratix10/Agilex 7 配置流程如下:

Step1:上电 (Power UP)

Altera Stratix 10/Agilex 7 电源需根据电源管理用户指南中的器件的上电顺序要求进行供电。

电源达到正确操作电压后,一个器件范围 Power on Reset (POR) 会置位。在电源达到操作电压之前,外部电源斜坡 (ramp) 不得慢于最小斜坡速率 (ramping rate)。

配置期间,内部电路从内部拉低 SDM_IO0, SDM_IO8 和 SDM_IO16。内部电路将剩下的 SDM_IO 管脚拉至一个弱高电平。

POR 之后,内部电路也将所有的 GPIO 管脚拉至一个弱高电平,直到器件进入用户模式 (user mode)。

Step2:SDM 启动 (SDM Startup)

SDM 在上电期间对 MSEL 管脚进行采样。

如果 MSEL 设置为 JTAG,那么 SDM 保持在 Startup 状态。

SDM 运行存储在 on-chip boot ROM 中的固件,然后进入 Idle 状态,直到主机驱高 nCONFIG。在所有时钟稳定之前,主机不应该驱高 nCONFIG。

Step3:空闲 (Idle)

在外部主机通过将 nCONFIG 管脚从低电平驱动为高电平来启动配置之前,SDM 一直保持在 IDLE 状态。或者 SDM 在退出错误状态后进入空闲状态。

Step4:配置开始 (Configuration Start)

SDM 接收到一个配置启动请求(nCONFIG = HIGH)后, SDM 通过驱高 nSTATUS 管脚来表明配置开始。

接收到配置数据时, SDM 执行认证,解密和解压缩。

nCONFIG 管脚在配置期间和用户模式下保持为高电平。主机持续监控 nSTATUS 管脚以查找配置错误。

Step5:配置通过 (Configuration Pass)

SDM 在成功接收到完整比特流后驱高 CONF_DONE 管脚。

CONF_DONE 管脚向外部主机发出信号,表示比特流传输成功。

Step6:配置错误 (Configuration Error)

nSTATUS 管脚上的一个低脉冲表明一个配置错误。

错误要求重配置。

一个低脉冲 (表明一个错误) 后,配置停止。nSTATUS 管脚保持高电平。

发生错误后,SDM 在外部主机驱低 nCONFIG 之后驱低 nSTATUS。

nSTATUS 管脚恢复到初始预配置低状态后,器件进入 Idle 状态。

Step7:用户模式 (User Mode)

初始化内部寄存器后,SDM 将 INIT_DONE 管脚驱动为高电平,并从高阻抗状态释放 GPIO 管脚。器件进入用户模式。整个器件不会同时进入用户模式。Altera 要求在设计中包括 Reset Release。使用 Reset Release Altera FPGA IP 的 nINIT_DONE 输出将应用逻辑保持在复位状态,直到整个 FPGA 架构处于用户模式。如果此 IP 没有包含在设计中,那么可能会导致间歇性的应用逻辑故障。

nCONFIG 管脚应该在用户模式下保持高电平。

通过将 nCONFIG 管脚从低电平驱动到高电平,可以对器件进行重配置。

Step8:器件清理 (Device Clean)

在 Device Clean 状态中,设计停止运行。

器件清理 (device cleaning) 清除所有配置数据。

器件驱低 CONF_DONE 和 INIT_DONE。

当器件清理 (device cleaning) 完成后,SDM 驱低 nSTATUS 管脚。

图2 配置流程

如下图 (图3) 所示为配置时序。图的第一部分显示了正常上电复位后初始配置的预期时序。最初,应用逻辑驱低 nCONFIG 信号 (POR)。在正常情况下,nSTATUS 在nCONFIG 后面,因为 nSTATUS 反映了当前配置状态。nCONFIG 的值只有在与 nSTATUS 的值相同时才可以更改。当出现错误时,nSTATUS 拉低大约 1ms,当器件准备好接受重配置时置位高电平。时序图中的初始配置部分中的数字标记以下事件:

1. SDM 启动并采样 MSEL 信号以确定指定的 FPGA 配置方案。在下一次上电之前,SDM 不再对 MSEL 管脚进行采样。

2. 当 nCONFIG 信号为低电平时,SDM 引导后进入 Idle 模式。

3. 当外部主机驱高 nCONFIG 信号时,SDM 启动配置。SDM 驱高 nSTATUS 信号,表示 FPGA 配置的开始。SDM 接收 MSEL 总线在 Step 1中指定的接口上的配置比特流。上图显示了 AVST_READY 和 AVST_VALID 持续为高电平。AVST_READY 可以置低,这要求 AVST_VALID 在六个周期内置低。

4. SDM 驱高 CONF_DONE 信号,表明 SDM 成功接收到了比特流。

5. 当 FPGA 置位 INIT_DONE,表明 FPGA 已经进入用户模式 (user mode)。GPIO 管脚退出高阻抗状态。CONF_DONE 与INIT_DONE 的置位之间的时间是可变的。对于 FPGA 第一次配置,INIT_DONE 在 FPGA 架构的初始化 (包括寄存器和状态机) 后置位。对于 HPS 第一次配置,HPS 应用控制 CONF_DONE 与 INIT_DONE 之间的时间。运行在 HPS 上的软件 (如 U-Boot) 或者操作系统 (OS) 启动配置,FPGA 配置并进入用户模式后, INIT_DONE 才置位。

图3 配置时序图

典型问题案例解析与解决方案

案例一:JTAG 识别器件异常 (PCN:1SX085H3F43E2VG)

问题描述:

在客户设计中,SmartVID 电源 VCC/VCCP 与 0.9V 电源 VCCERAM/VCCPLLDIG_SDM 共用电源轨,导致 JTAG 识别不到器件。

解决方案:

把两个电源轨分开即可正常识别器件。

图4 案例一图示

案例二:PMBUS 调压失败 (PCN:1SX085H3F43E2VG)

问题描述:

客户选用的某国产电源芯片,电源芯片支持的调压方式为 Step,其调压步长定义为 1LSB = RA*0.5uA,一般的电源芯片是 1LSB = 1mV,我们器件通过 PMBUS 设置的为 Final Vout,导致调压不成功。

解决方案:

目前短期通过 INI 文件绕过 PMBUS,手动设置固定电压,后续更换为兼容 PMBUS 的电源芯片。

图5 案例二图示

案例三:FPGA 断电重启失效 (PCN:1SX085H3F43E2VG)

问题描述:

加载 JIC 配置文件后,设备断电重启时 FPGA 无法正常完成配置。经分析,故障原因为客户电路板上的主控芯片对上电时序逻辑处理异常。具体表现为:

电源时序冲突:

(1) 系统上电顺序为主控芯片优先启动,目标 FPGA (Stratix10) 延迟上电。

(2) 主控芯片完成初始化后,立即将 nCONFIG 信号置为高电平,而非在 FPGA 的 IDLE 状态阶段触发该信号。

配置流程失效:

目标 FPGA 在 IDLE 阶段未检测到 nCONFIG 的有效上升沿,导致配置状态机未能激活,后续配置过程中断。

解决方案:

主控芯片上电不要去操作 nCONFIG,通过外部电路操作,上电 Flash 能够加载,需要 reconfig 时再通过主控芯片进行操作。

图6 案例三图示

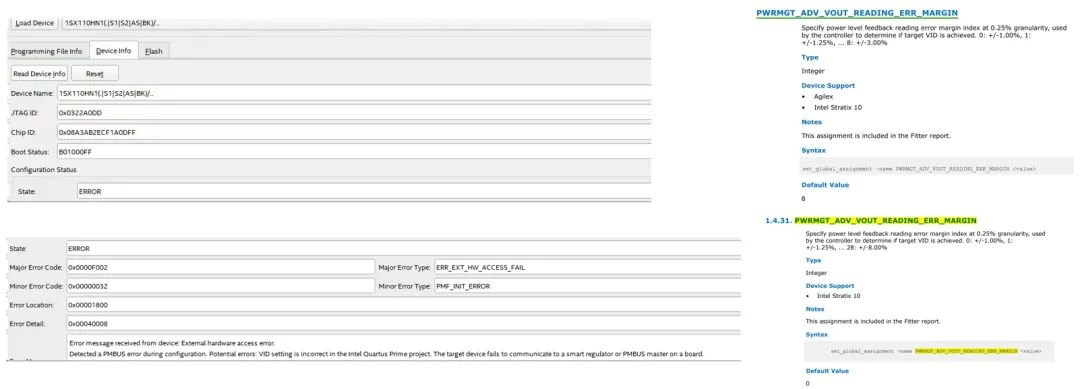

案例四:HPS First 模式加载概率性失败 (PCN:1SX110H1F43E2VG)

问题描述:

在 HPS First 启动模式下,系统通过 HPS 加载 FPGA 程序,FPGA 程序存储在 NAND flash。在测试中发现:

在测试中的 10 块板子中,有两块存在断电重启之后 FPGA 概率性无法启动现象,有时候可以启动,有时无法启动。但通过 JTAG 加载 FPGA first 模式后,都能够启动。

所有的板子初始供电电压都是 0.9V,通过示波器观察异常板子 VID 调压后,实际电压被调到了 0.94V,初始电压值和调压值压差过大,超过了默认的 ±3% (老版本最大限制为 ±3%,22.4 版本之后可以调到 ±8%)。

解决方案:

确认异常板卡固件版本,若低于 22.4 需更新版本到 22.4 或者 23.1,通过添加约束 set_global_assignment -name PWRMGT_ADV_VOUT_READING_ERR_MARGIN 28,把压差扩大到 8%。

Intel Quartus Prime Pro Edition Settings File Reference Manual(点击阅读原文此处了解)

图7 案例四图示

案例五:电源瞬态欠压保护 (PCN:AGFB027R24C2E1V)

问题描述:

本案例中使用到的电源芯片为:ADI LTM4680,当 FPGA 在下载大逻辑资源量 *.sof 的情况时 (60%以上),下载到 99% 时会显示失败。经过排查发现,当下载失败时,FPGA 的整板四组电源 RUN 使能管脚均被拉低断电。

由于板级存在上电时序管理芯片,一旦第一组核电发生异常,上电时序管理芯片会触发保护机制,后级将全部被关闭。为验证此问题,我们将上电时序改为 CPLD 独立控制。在此配置下,发现核电会出现短暂的“掉坑”现象,大约持续 240ms。通过与 ADI 电源厂家沟通,利用上位机工具对 FPGA 下载过程中的电源状态进行实时监控,成功复现了这一现象。

经过反复测试,抓取到电源异常时报出的一个输出欠压警告信息,经过 ADI 的 AE 和我们的 AE 一起分析,确认问题的根本原因为:在负载剧烈变化时,电源输出电压出现瞬态欠压,进而触发保护机制。

解决方案:

通过调整电源管理器的输出欠压保护阈值,将欠压门限从默认值降低至 0.2V,逻辑版本为 66% 和 70% 的资源量均可成功下载,电源系统也未再出现瞬态“掉坑”现象。

图8 案例五图示

案例六:MBR 配置错误导致 JTAG 加载失败 (PCN:AGFB014R24B2E2V)

问题描述:

通过 jtag 加载 sof 文件时,加载到 35% 时会显示失败。经过分析,将问题定位在 MBR 配置不对,具体表现为:客户使用的电源芯片精度为 1LSB = 2mV,而当 MBR = 100 时,实际需要 1LSB = 1mV 的精度,两者存在规格不匹配的情况。

解决方案:

目前为客户提供了绕过 PMBUS 的 ini 文件,确保客户可先正常调试功能,同时也与电源芯片供应商进行技术沟通,以确定 MBR 参数的最佳配置方案。

图9 案例六图示

Altera Stratix10 和 Agilex 7

电源配置问题检查方向

检查方向

jtag 加载失败问题:首先要检查 quartus 配置参数是否与电源芯片相符,包括电源引脚,PMBUS 地址,MBR 参数设置值以及 valid unit 和 mode 等

器件识别异常:确认供电是否满足 datasheet 要求以及 pcg 要求

Flash 加载异常和加载之后不工作:检查 MSEL 配置是否正确,以及 nconfig,nstatus,configdone,initial done 是否正常

Debug

每家电源厂家都有上位机软件监控电源状态,异常时可以通过电源上位机软件抓取电源状态,查看异常情况

Quartus 提供了config debug 工具,异常时可以看到在什么阶段异常,错误码是什么,然后进行分析

如果是 PMBUS 问题,且暂时没有解决方案,可以提供绕过 PMBUS 的方法让客户先进行功能调试,这样不会阻塞客户调试进度 (该方案实测在最新版本 23.2 以及 agilex 上可用)

最重要一点是客户投板之前一定要进行原理图 review 和 pin map 验证

总结

本文通过列举 Altera Stratix10 和 Agilex 7 FPGA 在客户实际应用中遇到的电源管理及配置问题案例,为大家系统梳理了典型的故障问题分析,同时给出相应的解决方案与调试建议,供工程师们参考。

-

FPGA

+关注

关注

1644文章

21989浏览量

615232 -

英特尔

+关注

关注

61文章

10182浏览量

174137 -

电源管理

+关注

关注

117文章

6411浏览量

145892 -

Altera

+关注

关注

37文章

803浏览量

155637 -

Agilex

+关注

关注

0文章

15浏览量

3839

原文标题:Altera Stratix®10 和 Agilex™ 7 电源配置问题案例解析

文章出处:【微信号:骏龙电子,微信公众号:骏龙电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于Altera Agilex™ 7 400G Ethernet IP 与FPC202芯片控制使用手册

浅析Altera公司Stratix V FPGA芯片

二手FPGA

Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?

Altera Stratix IV FPGA助推XDI db

Altera推出面向Stratix IV FPGA的最新开发

Altera Stratix IV FPGA继续广受全球媒体

Altera推出业界带宽最大的28nm Stratix V

Altera助推客户启动14 nm Stratix 10 FPGA和SoC设计

业界密度最大的Stratix IV EP4SE820 FPGA(Altera)

深度解读:Intel最新的FPGA Agilex

具有LVDS输出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

Altera Agilex 7 M系列FPGA正式量产出货

Altera Agilex 3 FPGA和SoC产品介绍

Altera Stratix 10和Agilex 7 FPGA的电源管理及配置问题案例

Altera Stratix 10和Agilex 7 FPGA的电源管理及配置问题案例

评论